1. 概述

在本篇文章中,我们将简要介绍两种主流 CPU 架构设计的优缺点:精简指令集计算(RISC)与复杂指令集计算(CISC)。

从上世纪 80 年代起,关于 CPU 设计方式的争论就从未停止。一部分人主张通过少量复杂指令完成复杂任务(CISC),另一部分人则主张通过大量简单指令来实现高性能(RISC)。

随着摩尔定律的演进,芯片晶体管数量持续增长,硬件设计复杂度成为制约因素。RISC 因其架构简洁、实现成本低、开发周期短,逐渐成为主流。但 CISC 也在不断吸收 RISC 的设计理念,两者界限已逐渐模糊。

2. RISC vs. CISC

| 对比维度 | RISC | CISC |

|---|---|---|

| 设计理念 | 简单指令,强调软件优化 | 复杂指令,强调硬件功能 |

| 每条指令周期数 | 少,多数指令在单周期完成 | 多,不同指令周期差异大 |

| 代码体积 | 较大 | 较小 |

| 晶体管用途 | 更多用于寄存器 | 更多用于复杂指令逻辑 |

| 典型指令集 | ARM、RISC-V、PowerPC、SPARC | x86 |

| 执行方式 | Load/Store 架构 | Memory-to-Memory 架构 |

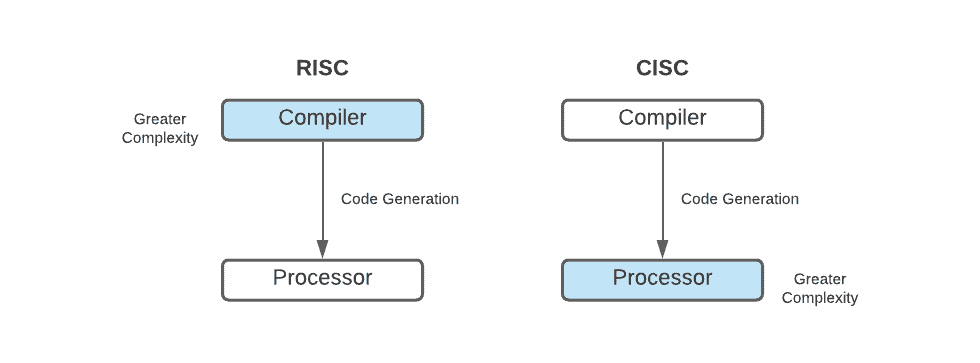

以下是一张形象地展示 RISC 与 CISC 区别的示意图:

3. RISC 架构

RISC(Reduced Instruction Set Computing) 是一种 CPU 设计理念,主张通过简化指令集,使每条指令都能在单个时钟周期内完成,从而提高整体执行效率。

RISC 的理念由 David Patterson 和 John Hennessy 提出,其核心在于通过简化硬件设计,将复杂度转移至编译器和软件层。

3.1. 主要设计原则

✅ 指令集限制:仅提供少量基础指令,如加法、位移等,复杂操作由多个基础指令组合而成

✅ 通用寄存器:所有寄存器均可用于数据或地址存储,提高访问效率

✅ 流水线设计:将指令执行拆分为多个阶段,实现并行处理

✅ Load/Store 架构:数据处理仅在寄存器间进行,内存访问通过独立的 Load 和 Store 指令完成

这些设计使得 RISC 处理器结构更简单,时钟频率更高,适合高性能、低功耗场景。

3.2. RISC 的优势

- ✅ 芯片面积和能耗更优,适合移动设备(如 ARM 处理器)

- ✅ 编译器更容易生成高效代码

- ✅ 寄存器用于参数传递和局部变量存储,提升性能

- ✅ 指令固定长度,易于流水线并行处理

- ✅ 执行速度快,指令周期短

3.3. RISC 的劣势

- ❌ 性能高度依赖编译器质量

- ❌ 编译器需要处理更多底层细节,实现复杂度高

4. CISC 架构

CISC(Complex Instruction Set Computing) 是早期 CPU 设计的主流方式,其目标是通过一条复杂指令完成更多操作,从而减少程序中的指令总数。

CISC 的设计初衷是为了减少内存使用,通过将多个操作合并为一条指令,降低程序对内存容量的需求。

4.1. CISC 的优势

- ✅ 单条指令功能强大,完成相同任务所需指令更少

- ✅ 代码体积小,节省内存空间

4.2. CISC 的劣势

- ❌ 多数复杂指令实际使用频率低

- ❌ 指令执行周期差异大,影响整体性能

- ❌ 硬件复杂度高,不利于高频运行

5. RISC 与 CISC 的核心区别图解

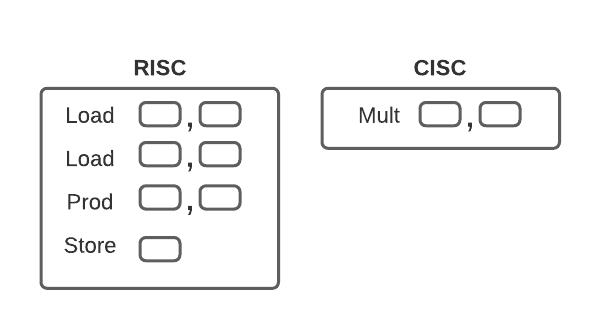

以下是一个乘法操作在 RISC 与 CISC 架构下的执行过程对比:

CISC 方式

- 使用一条复杂指令

MULT,直接操作内存中的两个数 - 不需要手动加载或存储数据,类似高级语言的一行代码

RISC 方式

- 需要三条指令:

LOAD:将内存数据加载到寄存器PROD:执行乘法运算STORE:将结果写回内存

这种设计虽然增加了指令数量,但每条指令都可在单周期内完成,提高了整体效率。

6. 总结

RISC 与 CISC 代表了 CPU 架构设计的两种哲学:

- RISC 强调简单、高效、可扩展,适合现代高性能、低功耗场景(如移动设备)

- CISC 强调功能集成、代码紧凑,适合早期资源受限的系统

随着技术发展,两者界限逐渐模糊。现代 CISC 处理器(如 x86)已广泛采用 RISC 内核 + 微码翻译的方式运行,而 RISC 架构也不断演进,如开源的 RISC-V 架构正逐步挑战 ARM 的市场地位。

✅ 踩坑提醒:理解 RISC 和 CISC 的区别有助于我们在选择处理器平台时做出更合理的技术决策。比如在嵌入式系统中优先考虑 RISC,而在传统 PC 领域仍以 CISC 为主。